# BSTP10K50 Programmable Logic Array Circuit Military Product Manual

#### **Table of contents**

- Product description

- Product Overview

- Product Features

- Product use and application scope

- Corresponding substitution of foreign products

- Product dimensions/actual photos

- Standard Implementation

- Brief description of basic working principle

- Circuit Function Block Diagram

- Package and Pin Description

- Functional Description

- Extreme working conditions and recommended working conditions

- Main technical parameters

- Electrical characteristic parameters

- Key Parameter Timing Diagram/Typical Application Peripheral

- ESD Characeristics

- FAQ

- Precautions

- Product Transportation and Storage Precautions

- Product Unpacking and Inspection

- Precautions for circuit operation

- Illustrate

- 9.1 After-sales service and guarantee

- 9.2 Contact Information

- 9.3 Version and Disclaimer

## **Product description**

## **Product description**

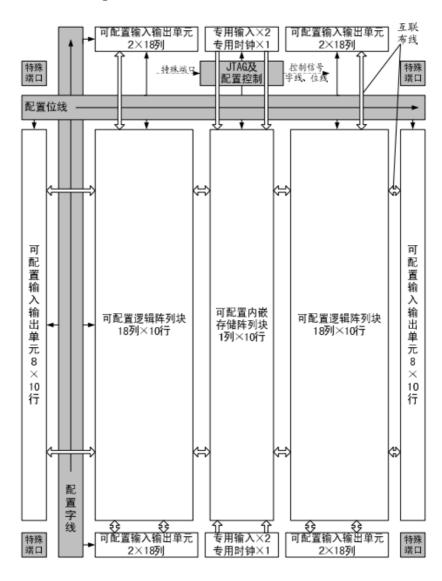

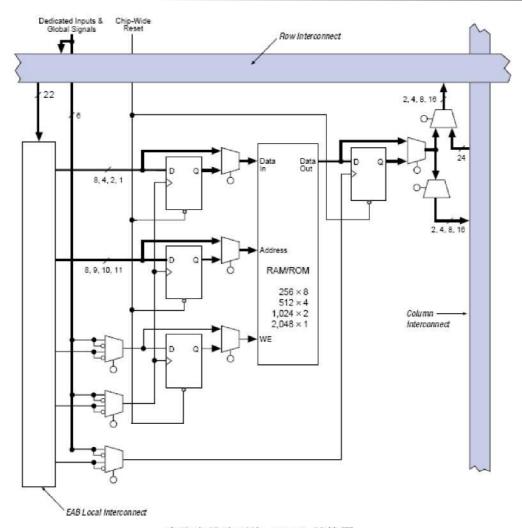

The BSTP10K50Q240-4type programmable logic array circuit is a high-density programmable logic array circuit based on SRAM configuration. The circuit consists of two parts: control circuit and configurable resources. The control circuit includes JTAG circuit, configuration control circuit, word line, bit line, and configuration data storage unit (SRAM). The configurable resources include configurable logic array block (LAB), configurable embedded storage array block (EAB), and configurable input and output unit (IOE). The configurable resources are interconnected through configurable row and column wiring distributed among them.

The circuit standard configurable gate count (logic and storage) is 50 000, and the maximum system gate count is 116 000. The configurable resources include 360 logic array blocks (LABs), 2880 logic elements (LEs), and 20480 bits of embedded storage array blocks (EABs), supporting four configuration modes: JTAG, passive serial, synchronous, and asynchronous passive parallel.

#### **Product features**

- This circuit is fully pin and functionally compatible with the EPF10K50RC240-4 circuit.

- Supports programmable system-on-chip architecture.

- Embedded arrays support large functional logic, such as specialty memories and specialized logic functions.

- Logic arrays support general combinational logic functions.

- high density

- 50 000 typical gate count.

- Up to 20K RAM capacity, each embedded logic block (EAB) size is 2048 bits, the

use of all EABs does not reduce the logic capacity.

- System Level Features

- Multi-level I/O interface.

- 3.3V/5V level input pin.

- Low power consumption design.

- Built-in JTAG boundary scan test circuit structure, according to IEEE standard

1149.1-1990, does not affect any device logic when used.

- Flexible internal wiring

- Distributed carry chains implement arithmetic logic functions such as adders, counters, and comparators (automatically called by software tools and large functions).

- Distributed cascade chains complete high-speed, high fan-in logic functions (automatically called by software tools and large functions).

- Two global clock signals.

- Complete I/O pins

- Each pin has independent three-state output enable control.

- Each I/O pin can be selected as open-drain.

- Programmable output slew rate control to reduce switching noise.

## Product use and application range

The internal structure of the BSTP10K50 circuit enables the circuit to realize complex logic functions (digital logic replacement below 50,000 gates).

Implement digital processors, microcontrollers, decoders, counters, small-scale memories, multiplexers, data transmission converters

Exchange and some simple algorithm logic.

#### Corresponding to the situation of replacing foreign products

It corresponds to the EPF10K50 circuit of the foreign Altera company. The two have the same functions, but are slightly inferior to foreign products in speed. The package is pluggable and replaceable (the shell size is slightly larger than that of foreign products), and the reliability has been improved to military grade.

## Product dimensions/Real photos

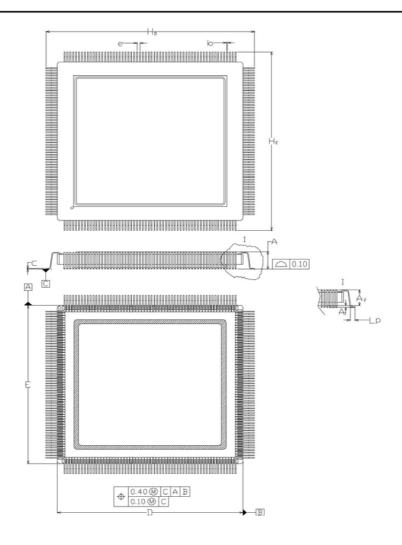

The circuit uses a 240-lead ceramic quad flat package (CQFP240). The specific dimensions are shown in Table 1.

Table 1.

Unit: mm

| Size code | size    |    |         |  |  |  |  |  |

|-----------|---------|----|---------|--|--|--|--|--|

|           | Minimum |    | Minimum |  |  |  |  |  |

|           |         |    |         |  |  |  |  |  |

| Α         | _       | A  | _       |  |  |  |  |  |

| A1        | 0.20    | A1 | 0.20    |  |  |  |  |  |

|           |         |    |         |  |  |  |  |  |

| A2        | _       | A2 | _       |  |  |  |  |  |

|           |         |    |         |  |  |  |  |  |

| b         | _       | b  | _       |  |  |  |  |  |

|           |         |    |         |  |  |  |  |  |

| С         | 0.10    | С  | 0.10    |  |  |  |  |  |

# **Standard Implementation**

The product quality grade is B, and the assessment standard complies with Q/FC 30020-2009 "BSTP10K50 Circuit Detailed Specification"

Requirements and meet GJB597 "General Specification for Semiconductor Integrated Circuits" and GJB548B-2005 "Test Methods and Procedures for Microelectronic Devices" The requirements of the Preface.

## Brief description of basic working principle

## **Circuit Function Block Diagram**

## **Package and Pin Description**

The circuit is packaged with the cover facing downwards and the heat sink on the front. The bottom picture shows the circuit with the front side (where the heat sink is) facing upwards.

BSTP10K50Q240-4circuit pin arrangement diagram

Among the 240 pins of the circuit, there are 189 user-configurable IO ports (167 user-configurable IO ports, 2 user-configurable dedicated clock input ports, 4 user-configurable dedicated input ports, 16 configuration/user IO dual-purpose ports), 5 JTAG dedicated ports, 9 dedicated configuration ports, 19 power ports, and 18 ground ports. See Table 3-Table 7 for pin definitions.

Table 3. BSTP10K50Q240-4Circuit pin definition

| Serial<br>number | Pin Symbols | I/O/Z |                      | Serial<br>number | Pin Symbols | I/O/Z | Function  |

|------------------|-------------|-------|----------------------|------------------|-------------|-------|-----------|

| 1                | TCK         | I     | JTAG Port            | 39               | Ю           | Ю     | User Port |

| 2                | CONF_DONE   |       | Configuring<br>Ports | 40               | Ю           | Ю     | User Port |

| 3                | CEO          |       | Configuring Ports          |       | Ю               |           | IO  | User Po | ort               |

|------------------|--------------|-------|----------------------------|-------|-----------------|-----------|-----|---------|-------------------|

| 4                | TDO          | 0     | JTAG Port                  | 42    | GN              | D         | l   | power s | supply            |

| 5                | VCC          |       | power supply               | 43    | Ю               |           | IO  | User Po | ort               |

|                  | Ю            | Ю     | User Port                  | 4     | 44              | IO        |     | IO      | User Port         |

| 7                | Ю            | Ю     | User Port                  | 4     | 45              | Ю         |     | Ю       | User Port         |

| 8                | 10           | Ю     | User Port                  | 4     | 46              | Ю         |     | Ю       | User Port         |

| 9                | Ю            | Ю     | User Port                  | 4     | 47              | VCC       |     | l       | power supply      |

| 10               | GND          | I     | power supply               | 4     | 48              | Ю         |     | Ю       | User Port         |

| 11               | CLKUSR/IO    | I/IO  | Configuration/<br>dual use | user, | 49              | Ю         |     | Ю       | User Port         |

| 12               | 10           | IO    | User Port                  |       | 50              | Ю         |     | Ю       | User Port         |

| 13               | 10           | IO    | User Port                  |       | 51              | Ю         |     | IO      | User Port         |

| 14               | IO           | Ю     | User Port                  |       | 52              | GND       |     | l       | power supply      |

| 15               | 10           | Ю     | User Port                  |       | 53              | Ю         |     | 10      | User Port         |

| 16               | VCC          | I     | power supply               |       | 54              | Ю         |     | 10      | User Port         |

| 17               | 10           | Ю     | User Port                  | 4     | 55              | IO        |     | Ю       | User Port         |

| 18               | Ю            | Ю     | User Port                  | ,     | 56              | Ю         |     | Ю       | User Port         |

| 19               | 10           | Ю     | User Port                  | ,     | 57              | VCC       |     | l       | power supply      |

| 20               | 10           | Ю     | User Port                  | ,     | 58              | TMS       |     | l       | JTAG Port         |

| twenty<br>one    | Ю            | Ю     | User Port                  | ļ     | 59              | TRST      |     | I       | JTAG Port         |

| twenty<br>two    | GND          | I     | power supply               |       | 60              | STATUS    |     | Ю       | Configuring Ports |

| twenty<br>three  | RDYnBSY/IO   | O/IO  | Configuration/<br>dual use | user' | 61              | Ю         |     | Ю       | User Port         |

| rour             | 10           | Ю     | User Port                  |       | 62              | Ю         |     | Ю       | User Port         |

| 25               | 10           | Ю     | User Port                  |       | 63              | Ю         |     | Ю       | User Port         |

|                  | INIT_DONE/IO | O/IO  | Configuration/<br>dual use |       | 64              | Ю         |     | Ю       | User Port         |

|                  | VCC          | I     | power supply               |       | 65              | Ю         |     | 10      | User Port         |

|                  | Ю            | Ю     | User Port                  |       | 66              | Ю         |     | 10      | User Port         |

| 29               | Ю            | Ю     | User Port                  |       | 67              | Ю         |     | 10      | User Port         |

| 30               | Ю            | Ю     | User Port                  |       | 68              | Ю         |     | 10      | User Port         |

| 31               | Ю            | Ю     | User Port                  |       | 69              | GND       |     | l       | power supply      |

|                  | GND          | I     | power supply               |       | 70              | Ю         |     | Ю       | User Port         |

| 33               | 10           | Ю     | User Port                  | -     | 71              | Ю         |     | Ю       | User Port         |

| 34               | 10           | Ю     | User Port                  | -     | 72              | Ю         |     | Ю       | User Port         |

| 35               | 10           | Ю     | User Port                  |       | 73              | Ю         |     | Ю       | User Port         |

| 36               | 10           | Ю     | User Port                  |       | 74              | Ю         |     | Ю       | User Port         |

|                  | vcc          | I     | power supply               | •     | 75              | Ю         |     | Ю       | User Port         |

| 38               | 10           | Ю     | User Port                  |       | 76              | Ю         |     | Ю       | User Port         |

| Serial<br>number | Pin Symbols  | I/O/Z | Function                   |       | Serial<br>numbe | Pin Symbo | ols | I/O/Z   | Function          |

| 77               | VCC          | 1     | power supply               |       | 118             | Ю         |     | Ю       | User Port         |

|                  | Ю            | 10    | User Port                  |       | 119             | Ю         |     | Ю       | User Port         |

| 79               | 10           | 10    | User Port                  |       | 120             | Ю         |     | Ю       | User Port         |

| 80               | Ю            | Ю     | User Port                  |       | 121             | nCONFIG   |     | l       | Configuring Ports |

| 81  | Ю    | IO User Port |       | 122              | VCC | I     | power supply |                   |

|-----|------|--------------|-------|------------------|-----|-------|--------------|-------------------|

| 82  | Ю    |              | Ю     | User Port        | 123 | MSEL1 |              | Configuring Ports |

| 83  | Ю    | Ю            | Us    | ser Port         | 124 | MSEL0 | I            | Configuring Ports |

| 84  | Ю    | Ю            | Us    | ser Port         | 125 | GND   | l            | power supply      |

| 85  | GND  | I            | powe  | power supply     |     | Ю     | Ю            | User Port         |

| 86  | Ю    | Ю            | Us    | ser Port         | 127 | Ю     | Ю            | User Port         |

| 87  | Ю    | Ю            | Us    | ser Port         | 128 | 10    | Ю            | User Port         |

| 88  | Ю    | Ю            | Us    | ser Port         | 129 | 10    | Ю            | User Port         |

| 89  | VCC  | I            | powe  | supply           | 130 | vcc   | I            | power supply      |

| 90  | DI   | 1            | Dedic | ated input       | 131 | Ю     | Ю            | User Port         |

| 91  | GCLK | I            | Dedic | ated clock input | 132 | Ю     | Ю            | User Port         |

| 92  | DI   | ı            | Dedic | ated input       | 133 | Ю     | Ю            | User Port         |

| 93  | GND  | 1            | powe  | supply           | 134 | Ю     | Ю            | User Port         |

| 94  | Ю    | Ю            | Us    | ser Port         | 135 | GND   | I            | power supply      |

| 95  | Ю    | Ю            | Us    | ser Port         | 136 | Ю     | Ю            | User Port         |

| 96  | VCC  | ı            | powe  | supply           | 137 | Ю     | Ю            | User Port         |

| 97  | Ю    | Ю            | Us    | ser Port         | 138 | Ю     | Ю            | User Port         |

| 98  | Ю    | Ю            | Us    | ser Port         | 139 | Ю     | Ю            | User Port         |

| 99  | Ю    | Ю            | Us    | ser Port         | 140 | vcc   | I            | power supply      |

| 100 | Ю    | Ю            | Us    | ser Port         | 141 | Ю     | Ю            | User Port         |

| 101 | Ю    | Ю            | Us    | ser Port         | 142 | Ю     | Ю            | User Port         |

| 102 | Ю    | Ю            | Us    | ser Port         | 143 | Ю     | Ю            | User Port         |

| 103 | Ю    | Ю            | Us    | ser Port         | 144 | Ю     | Ю            | User Port         |

| 104 | GND  | I            | powe  | supply           | 145 | GND   | I            | power supply      |

| 105 | Ю    | Ю            | Us    | ser Port         | 146 | Ю     | Ю            | User Port         |

| 106 | Ю    | Ю            | Us    | ser Port         | 147 | Ю     | Ю            | User Port         |

| 107 | Ю    | Ю            | Us    | ser Port         | 148 | Ю     | Ю            | User Port         |

| 108 | Ю    | Ю            | Us    | ser Port         | 149 | Ю     | Ю            | User Port         |

| 109 | Ю    | Ю            | Us    | ser Port         | 150 | vcc   | ı            | power supply      |

| 110 | Ю    | Ю            | Us    | User Port        |     | Ю     | Ю            | User Port         |

| 111 | Ю    | Ю            | Us    | User Port        |     | Ю     | Ю            | User Port         |

| 112 | VCC  | I            | powe  | power supply     |     | Ю     | IO           | User Port         |

| 113 | Ю    | Ю            | Us    | ser Port         | 154 | IO    | IO           | User Port         |

| 114 | Ю    | Ю            | Us    | ser Port         | 155 | GND   | ı            | power supply      |

| 115              | Ю              | Ю     | User Port                   | 156              | Ю           | Ю     | User Port                   |

|------------------|----------------|-------|-----------------------------|------------------|-------------|-------|-----------------------------|

| 116              | Ю              | Ю     | User Port                   | 157              | Ю           | Ю     | User Port                   |

| 117              | Ю              | Ю     | User Port                   | 158              | Ю           | Ю     | User Port                   |

| Serial<br>number | Pin<br>Symbols | I/O/Z | Function                    | Serial<br>number | Pin Symbols | I/O/Z | Function                    |

| 159              | Ю              | Ю     | User Port                   | 191              | Ю           | Ю     | User Port                   |

| 160              | VCC            | 1     | power supply                | 192              | Ю           | Ю     | User Port                   |

| 161              | Ю              | Ю     | User Port                   | 193              | Ю           | Ю     | User Port                   |

| 162              | Ю              | Ю     | User Port                   | 194              | Ю           | Ю     | User Port                   |

| 163              | Ю              | Ю     | User Port                   | 195              | Ю           | Ю     | User Port                   |

| 164              | Ю              | Ю     | User Port                   | 196              | Ю           | Ю     | User Port                   |

| 165              | GND            | I     | power supply                | 197              | GND         | I     | power supply                |

| 166              | Ю              | Ю     | User Port                   | 198              | Ю           | Ю     | User Port                   |

| 167              | Ю              | Ю     | User Port                   | 199              | Ю           | Ю     | User Port                   |

| 168              | Ю              | Ю     | User Port                   | 200              | Ю           | Ю     | User Port                   |

| 169              | Ю              | Ю     | User Port                   | 201              | Ю           | Ю     | User Port                   |

| 170              | VCC            | I     | power supply                | 202              | Ю           | Ю     | User Port                   |

| 171              | Ю              | Ю     | User Port                   | 203              | Ю           | Ю     | User Port                   |

| 172              | Ю              | Ю     | User Port                   | 204              | Ю           | Ю     | User Port                   |

| 173              | Ю              | Ю     | User Port                   | 205              | VCC         | I     | power supply                |

| 174              | Ю              | Ю     | User Port                   | 206              | Ю           | Ю     | User Port                   |

| 175              | Ю              | Ю     | User Port                   | 207              | Ю           | Ю     | User Port                   |

| 176              | GND            | I     | power supply                | 208              | Ю           | Ю     | User Port                   |

| 177              | TDI            | I     | JTAG Port                   | 209              | DEV_CLRn/IO | I/IO  | Configuration/user dual use |

| 178              | nCE            | I     | Configuring Ports           | 210              | DI          | I     | Dedicated input             |

| 179              | DCLK           | I     | Configuring Ports           | 211              | GCLK        | I     | Dedicated clock input       |

| 180              | DATA0          | I     | Configuring Ports           | 212              | DI          | I     | Dedicated input             |

| 181              | DATA1/IO       | I/IO  | Configuration/user dual use | 213              | DEV_OE/IO   | I/IO  | Configuration/user dual use |

| 182              | DATA2/IO       | I/IO  | Configuration/user dual use | 214              | Ю           | Ю     | User Port                   |

| 183              | DATA3/IO       | I/IO  | Configuration/user dual use | 215              | Ю           | Ю     | User Port                   |

| 184              | Ю              | Ю     | User Port                   | 216              | GND         | ı     | power supply                |

| 185              | DATA4/IO       | I/IO  | Configuration/user dual use | 217              | Ю           | Ю     | User Port                   |

| 186              | DATA5/IO       | I/IO  | Configuration/user dual use | 218              | Ю           | Ю     | User Port                   |

|                  |                |       |                             |                  |             |       |                             |

|               |   | 1              |       |              |                        | -                |    |             | 1     | 1                           |

|---------------|---|----------------|-------|--------------|------------------------|------------------|----|-------------|-------|-----------------------------|

| 187           | • | Ю              | Ю     | ι            | Jser Port              | 219              |    | Ю           | Ю     | User Port                   |

| 188           | 3 | DATA6/IO       | I/IO  | Cont<br>dual | figuration/user<br>use | 220              |    | Ю           | Ю     | User Port                   |

| 189           | ) | VCC            | - 1   | pow          | er supply              | 221              |    | Ю           | Ю     | User Port                   |

| 190           | ) | DATA7/IO       | I/IO  | Conf<br>dual | figuration/user<br>use | 222              |    | Ю           | Ю     | User Port                   |

| Seria<br>numb |   | Pin<br>Symbols | I/O/Z | Fund         | ction                  | Serial<br>number | •  | Pin Symbols | I/O/Z | Function                    |

| 223           | 3 | Ю              | Ю     | ι            | Jser Port              | 232              |    | GND         | I     | power supply                |

| 224           | ŀ | VCC            | I     | power supply |                        | 233              |    | Ю           | Ю     | User Port                   |

| 225           | 5 | Ю              | Ю     | User Port    |                        | 234              |    | Ю           | Ю     | User Port                   |

| 226           | 6 | Ю              | Ю     | ι            | Jser Port              | 235              |    | Ю           | Ю     | User Port                   |

| 227           | , | Ю              | Ю     | ι            | Jser Port              | 236              |    | nRS/IO      | I/IO  | Configuration/user dual use |

| 228           | Ю |                | 10    | 0            | User Port              | 237              | Ю  | )           | Ю     | User Port                   |

| 229           | Ю |                | I     | 0            | User Port              | 238              | n۷ | VS/IO       | I/IO  | Configuration/user dual use |

| 230           | Ю |                | 10    | 0            | User Port              | 239              | CS | S/IO        | I/IO  | Configuration/user dual use |

| 231           | Ю |                | 10    | 0            | User Port              | 240              | nC | CS/IO       | I/IO  | Configuration/user dual use |

Table 4. Function description of dedicated configuration port

| Pin Symbols    | User mode<br>usage | Configuration mode | Pin Type                           | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------|--------------------|--------------------|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

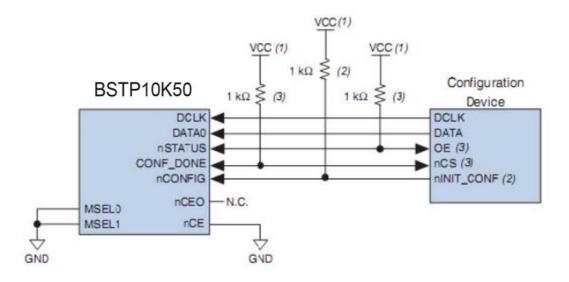

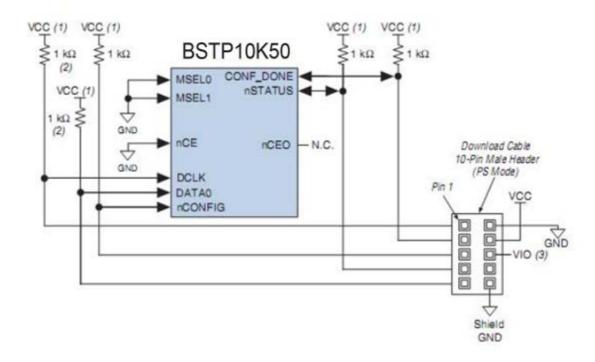

| MSEL0<br>MSEL1 | N/A                | all                | enter                              | Two-bit configuration mode selection signal input. The relationship between the input signal and the configuration mode is shown in Table 13. These two pins must be constantly valid after power-on until the end of the entire configuration process.                                                                                                                                                                         |

| nCONFIG        | N/A                | all                | enter                              | Configuration control signal input. Pulling this pin down in user mode will cause the FPGA to lose all configuration data and enter a reset state. All I/O pins are tri-stated. Pulling the pin back to a logic high state will initialize the FPGA to reconfigure.                                                                                                                                                             |

| nSTATUS        | N/A                | all                | Bidirecti<br>onal<br>open<br>drain | The FPGA pulls nSTATUS low immediately after power- on and releases it within 5µs. As a status output, if an error occurs during configuration, nSTATUS will be pulled low. As a status input. If an external source pulls nSTATUS low during configuration or initialization, the device enters the error state. Pulling nSTATUS low after configuration and initialization is complete does not affect the configured device. |

| CONF_DONE      | N/A                | all                | Bidirecti<br>onal<br>open          | The FPGA pulls the CONF_DONE pin low before and during configuration. Once all configuration data is received without error, the device enters the initialization state and the CONF_DONE pin is released and goes high. Pulling CONF_DONE low after configuration and                                                                                                                                                          |

|       |     |                                                      |        | initialization is complete will not affect the configured device.                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------|-----|------------------------------------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| nCE   | N/A | all                                                  | enter  | Chip enable signal, low effective. nCE goes low to allow configuration and activate the chip. The nCE pin must remain low during the configuration process, initialization process and user mode. It can be pulled down when configuring a single device. When multiple devices are chained, the nCE of the first configured device is pulled down and its nCEO is connected to the nCE of the next device in the chain. nCE must also remain low in the JTAG configuration mode. |

| CEO   | N/A | all                                                  | Output | Driven low when the device is configured. When configuring a single device, leave it unconnected. When configuring multiple devices in a chain, connect it to the nCE of the next device in the chain and leave the nCEO of the last device in the chain unconnected.                                                                                                                                                                                                             |

| DCLK  | N/A | Synchronous<br>configuration<br>process (PS,<br>PPS) | enter  | Clock signal input. Data is latched into the FPGA on the rising edge of DCLK. In PPA mode, DCLK should be pulled up to VCC to prevent it from floating. After configuration is complete, this pin is tri-stated.                                                                                                                                                                                                                                                                  |

| DATA0 | N/A | all                                                  | enter  | Data input. In serial configuration mode, the bit-width configuration data is passed                                                                                                                                                                                                                                                                                                                                                                                              |

Table 5. Relationship between MSEL0, MSEL1 and configuration mode

| MSEL1 | MSEL0 | Configuration Mode |

|-------|-------|--------------------|

| 0     | 0     | PS                 |

| 1     | 0     | PPS                |

| 1     | 1     | PPA                |

| 2     | 2     | JTAG ①             |

## Note:

- JTAG configuration has the highest configuration priority. When JTAG configuration is performed, the MSEL signal is ignored.

- After configuration is complete, do notMSELThe pins are left floating and connected to high or low levels.JTAGConfiguration mode, inJTAGJust ground them during configuration.

Table 6. Configuration/User IO dual-purpose port function description

| Pin Name     | User mode usage | Configuration mode     | Pin Type                                                                                                                       | Functional Description                                                                                                                                                                                                                                       |

|--------------|-----------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DATA<br>[71] | I/O             | Parallel<br>mode (PPS, | , enter                                                                                                                        | Data input. Bit-width configuration data enters the target device through DATA[70]. In serial configuration mode, these pins are used as user I/O pins during the configuration process and are left floating.                                               |

| [/]          |                 | PPA)                   |                                                                                                                                | After PPA or PPS configuration, DATA[71] are used as user I/O and their status depends on the setting of Dual_Purpose Pin option in software.                                                                                                                |

|              |                 |                        |                                                                                                                                | In PPA configuration mode, after nRS is selected, the DATA7 pin represents the RDYnBSY signal.                                                                                                                                                               |

| DATA7        | I/O             | PPA                    | Bidirectio                                                                                                                     | In serial configuration mode, the DATA7 pin is used as a user I/O pin during the configuration process and is left floating.                                                                                                                                 |

|              |                 |                        |                                                                                                                                | After PPA configuration, DATA7 is used as user I/O and its status depends on the setting of Dual_Purpose Pin option in software.                                                                                                                             |

|              |                 |                        |                                                                                                                                | Write strobe signal input. Its rising edge causes the device to latch one byte of data from DATA[71].                                                                                                                                                        |

| nW           | I/O             | PPA                    | enter                                                                                                                          | In non-PPA configuration mode, it is used as a user I/O pin during configuration and is left floating.                                                                                                                                                       |

|              |                 |                        | After PPA configuration, nWS is used as user I/O and its status depends on the setting of Dual_Purpose Pin option in software. |                                                                                                                                                                                                                                                              |

|              |                 |                        |                                                                                                                                | Read strobe signal input. When the input signal is low, the device will send the RDYnBSY signal to the DATA7 pin.                                                                                                                                            |

| ~D           | 1/0             | DDA                    | onto:                                                                                                                          | If the nRS pin is not used in PPA configuration pull it high.                                                                                                                                                                                                |

| nR           | I/O             | PPA                    | enter                                                                                                                          | In non-PPA configuration mode, it is used as a user I/O pin during configuration and is left floating.                                                                                                                                                       |

|              |                 |                        |                                                                                                                                | After PPA configuration, nRS is used as user I/O and its status depends on the setting of Dual_Purpose Pin option in software.                                                                                                                               |

|              |                 |                        | (<br>!<br>1                                                                                                                    | Ready to complete signal output. When the output signal goes high, it means the target device is ready to receive the next byte of data; when the output signal goes low, it means the target device is busy and not ready to receive the next byte of data. |

| RDY          | I/O             | PPS<br>PPA             | Output                                                                                                                         | In PPS and PPA configuration modes, this pin will be pulled high at power-on, before configuration starts, and after configuration ends before entering user mode.                                                                                           |

|              |                 |                        |                                                                                                                                | In non-PPS and PPA configuration modes, it is used as user I/O during the configuration process and is left floating.                                                                                                                                        |

|              |                 |                        |                                                                                                                                | After PPS or PPA configuration, RDYnBSY is used as user I/O and its status depends on the setting of Dual_Purpose Pin option in software.                                                                                                                    |

| nCS/CS       | I/O             | PPA 6                  |                                                                                                                                | Chip select signal input. The target chip is selected for configuration by inputting nCS low and CS high. During                                                                                                                                             |

|               |                                                                   |      |                      | configuration and initialization, the nCS and CS pins must remain valid.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------|-------------------------------------------------------------------|------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               |                                                                   |      |                      | In PPA configuration mode, only one of nCS or CS is needed to make the selection, and the unused pin is connected to a valid state. If nCS is grounded, the configuration process can be controlled by the jump of CS.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|               |                                                                   |      |                      | In non-PPA configuration mode, it is used as user I/O during the configuration process and is left floating.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|               |                                                                   |      |                      | After PPA configuration, nCS and CS are used as user I/O, and its status depends on the setting of Dual_Purpose Pin option in software.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| CLKUSD        | Software<br>setting on:<br>N/A                                    | all  |                      | Optional user initialization clock input. Can be used to synchronize the initialization of one or more devices.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|               | Software<br>setting off:<br>I/O                                   | a.i. | onto                 | This pin can be enabled by turning on the Enable user-<br>suoolied start-up option in the QuartusII software.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| INIT_<br>DONE | Software<br>setting on:<br>N/A<br>Software<br>setting off:<br>I/O |      | Output<br>open drain | Status output pin. It can be used to identify whether the device has completed initialization and entered user mode. When the nCONFIG pin is low at the beginning of configuration, the INIT_DONE pin is tri-stated and pulled up by an external $1k\Omega$ resistor. Once the control word that enables INIT_DONE is written into the device (the control word is the beginning segment of the configuration data), INIT_DONE will go low. When initialization is completed, INIT_DONE will be released and pulled up, and the FPGA will enter user mode. Therefore, if there is a monitoring circuit, it must be able to detect the low-to-high jump. |

|               |                                                                   |      |                      | This pin can be enabled by turning on the Enable INIT_DONE option in the QuartusII software.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| DEV OF        | Software<br>setting on:<br>N/A                                    | all  | enter                | Selectable pin allows the user to control all tri-states of the device. When this pin is pulled down, all I/Os are tri-stated; when this pin is pulled up, all pins work as configured.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|               | Software<br>setting off:<br>I/O                                   | all  | ,                    | This pin can be enabled by turning on the Enable devicewide output enable (DEV_OE) option in the QuartusII software.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| DEV_CLRn      | Software<br>setting on:<br>N/A<br>Software<br>setting off:        | all  | enter                | Optional pin allows the user to control the clearing of all registers. When this pin is pulled down, all registers are cleared; when this pin is pulled up, all registers work as set. This pin can be enabled by turning on the Enable device-                                                                                                                                                                                                                                                                                                                                                                                                         |

|               | I/O                                                               |      |                      | wide reset (DEV_CLRn) option in the QuartusII software.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

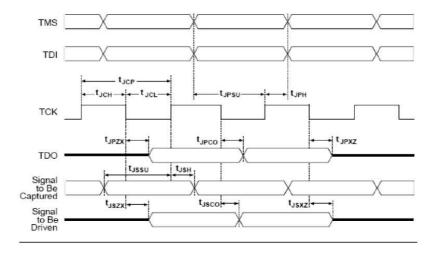

Table 7. JTAG dedicated port function description

| Pin Name | User mode<br>usage | Pin<br>Type | Functional Description                                                                                                                                                                                                                                                                                                                                     |

|----------|--------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TDI      | N/A                | enter       | JTAG instruction, test data, and configuration data serial input pin. Data is shifted on the rising edge of TCK.  If the JTAG interface is not used in the circuit, connect TDI to VCC to disable the JTAG circuit.                                                                                                                                        |

| TDO      | N/A                | Output      | JTAG instruction, test data, and configuration data serial output pin. Data is shifted on the falling edge of TCK. This pin is tristated when no data is being shifted out of the device. If the JTAG interface is not used in the circuit, leave TDO floating to disable the JTAG circuit.                                                                |

| TMS      | N/A                | enter       | Provides a control signal input pin that determines the TAP state machine flip. The TAP state machine flips on the rising edge of TCK. Therefore, TMS must be set before the rising edge of TCK arrives. TMS will be sampled on the rising edge of TCK.  If the JTAG interface is not used in the circuit, connect TMS to VCC to disable the JTAG circuit. |

| тск      | N/A                | enter       | JTAG clock input signal. Some operations occur on the rising edge of TCK, and some on the falling edge. If the JTAG interface is not used in the circuit, connect TCK to GND to disable the JTAG circuit.                                                                                                                                                  |

| TRST     | N/A                | enter       | Active low input used to synchronize the reset of the boundary scan circuitry. The TRST pin is optional per IEEE Std. 1149.1. If the JTAG interface is not used in the circuit, connect TRST to GND to disable the JTAG circuit.                                                                                                                           |

## **Functional Description**

The circuit itself has no fixed logic functions, and its operation is divided into two main stages: configuration mode and user mode. In configuration mode, under the action of the configuration control circuit, the configuration data is written into the SRAM through the word line and bit line. The data determines the function and connection relationship of the circuit's configurable resources. After all the data is written, it enters the user mode to realize the configured function. The SRAM can be repeatedly erased and written to realize different circuit functions.

The internal structure consists of two parts: control circuit and configurable resources. The control circuit includes JTAG circuit, configuration control circuit, word line, bit line, and configuration data storage unit (SRAM); the configurable resources include configurable logic array block (LAB), configurable embedded memory array block (EAB), and configurable input and output unit (IOE). The configurable resources are connected to each other through configurable row and column wiring distributed among them.

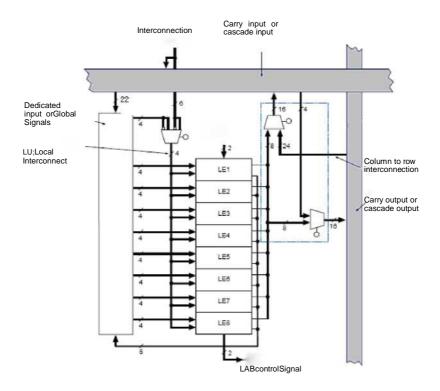

## Logic Array Block (LAB)

The logic array of BSTP10K50 consists of logic array blocks (LABs), each of which contains eight logic elements (LEs), carry chains and cascade chains associated with the LEs, LAB control signals, and LAB local interconnects. These eight LEs can be used to implement medium-sized block logic - 8-bit counters, address decoders, or state machines - or to implement larger logic blocks through the combination of multiple LABs. See figure.

## Configurable general purpose input and output units (Input/Output ELEMENT, IOE)

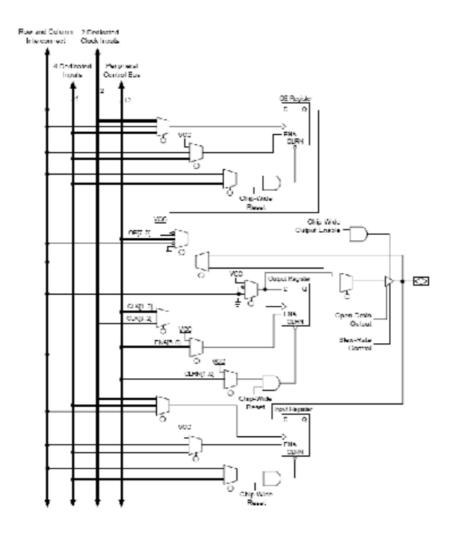

The configurable general-purpose input and output unit (IOE) provides an interface between the chip's external pins and internal logic functions. Each general-purpose input/output pin of the chip corresponds to an IOE. There are 304 general purpose IOE resources in the chip, including 72 in the upper and lower parts and 80 in the left and right parts. IOE can realize the data exchange function inside and outside the chip under the control of internal logic and external ports. The IOE structure is shown in the figure.

Input and output unit (IOE)

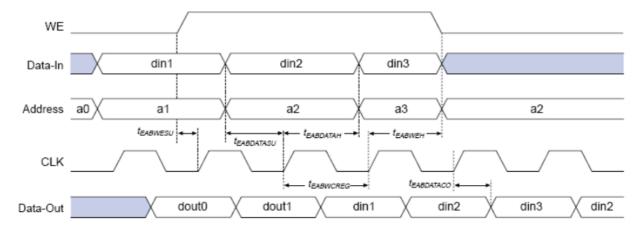

## **Embedded Storage Array Embedded array block, EAB)**

The embedded array contains 10 EABs, each with a capacity of 2048 bits and a total capacity of 20480 bits. When used as a memory, it can be used as RAM, ROM, dual-port RAM, or FIFO. When configured as a logic function, it can be used for complex logic functions of 100 to 600 gates, such as multipliers, microcontrollers, state machines, and DSP chips. The EAB array can be used alone, or multiple EABs can be combined to form a larger logic function. The figure shows the structure of the embedded storage array block (EAB).

内嵌存储阵列块 (EAB) 结构图

# Extreme working conditions and recommended working conditions

## **Extreme working conditions**

| Parameter name            | Parameter range | unit |

|---------------------------|-----------------|------|

| Supply voltage            | -1.0~6.5        | V    |

| I/O input voltage         | -1.0~6.5        | V    |

| Storage temperature range | -65~150         | °С   |

| Junction temperature      | 150             | °C   |

## **Recommended operating conditions**

| Parameter name              | Parameter range | unit |

|-----------------------------|-----------------|------|

| Operating temperature range | -55~125         | °C   |

| Device supply voltage       | 5±0.5           | V    |

| Port DC input voltage       | -0.5~VCC+0.5    | V    |

# **Main technical parameters**

## **Electrical characteristic parameters**

|            |                                              |                   | condition<br>(Unless otherwise        | Standard | value   |      |

|------------|----------------------------------------------|-------------------|---------------------------------------|----------|---------|------|

| characteri | stic                                         | symbol            | specified, VCC=5V,<br>-55°C≤TA≤125°C) | Minimum  | Maximum | unit |

|            | Supply current (standby)                     | ICC0              | VI=GND, no load                       |          | 10      | mΑ   |

|            | Input high level voltage                     | ин                |                                       | 2.0      | VCC+0.5 | V    |

|            | Input low level voltage                      | ИL                |                                       | -0.5     | 0.8     | V    |

| quiet      | Output high level voltage                    | <i>V</i> ОН       | /OH=-4mA DC,<br>VCC=4.75V             | 2.4      |         | V    |

| state      | Output low level voltage                     | <i>V</i> OL       | /OL=12mA DC,<br>VCC=4.75V             |          | 0.45    | V    |

| Ginseng    | Input pin leakage current                    | Л                 | M = VCC or GND                        | -10      | 10      | μΑ   |

| number     | Three-state input/output pin leakage current | ЮZ                | VO = VCC or GND                       | -40      | 40      | μΑ   |

|            | Input Capacitance a)                         | CIN               | VIN=0V, f=1.0MHz                      |          | 10      | pF   |

|            | Dedicated clock pin input capacitance a)     | CINCLK            | VIN=0V, f=1.0MHz                      |          | 15      | pF   |

|            | Output Capacitor a)                          | <b>∞</b> UT       | VOUT=0V, f=1.0MHz                     |          | 10      | pF   |

|            | Data Input LUT Delay                         | <i>t</i> LUT      |                                       |          | 1.8     | ns   |

|            | Carry Input LUT Delay                        | CLUT              |                                       |          | 0.6     | ns   |

|            | LE register feedback LUT delay               | <i>t</i> RLUT     |                                       |          | 2.0     | ns   |

|            | Data input to packed register delay          | tPACKED           |                                       |          | 0.8     | ns   |

|            | LE Register Enable Delay                     | <sup>t</sup> EN   |                                       |          | 1.5     | ns   |

| logic      | Carry-in to carry-out delay                  | tCICO             |                                       |          | 0.4     | ns   |

| Edit       | Data-in to Carry-out Delay                   | <sup>t</sup> CGEN |                                       |          | 1.4     | ns   |

| one        | LE register feedback to carry output delay   | CGENR             |                                       |          | 1.4     | ns   |

| Yuan       | Cascade Input to Cascade Output Delay        | tCASC             |                                       |          | 1.2     | ns   |

| L          | LE register control signal delay             | tC                |                                       |          | 1.6     | ns   |

| E          | LE Register Clock to Output Delay            | tCO               |                                       |          | 1.2     | ns   |

| hour | Combined Delay                                                                                                                                           | tCOMB            |   |     | 0.6 | ns |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---|-----|-----|----|

|      | The setup time of the LE register data and enable signal before the clock; The recovery time of the LE register after asynchronous clear, preset or load | <i>t</i> SU      |   | 1.4 |     | ns |

|      | LE register data and enable signal, hold time after clock                                                                                                | <i>t</i> H       |   | 1.3 |     | ns |

|      | LE register preset delay                                                                                                                                 | <sup>t</sup> PRE |   |     | 1.2 | ns |

| sdf  | LE register clear delay                                                                                                                                  | <sup>t</sup> CLR |   |     | 1.2 | ns |

| Mini | mum high time of clock pin                                                                                                                               | tCH.             | _ | 4.0 | r   | ıs |

| Mini | mum low time of clock pin                                                                                                                                | <i>t</i> CL      |   | 4.0 | r   | ıs |

|                          | •                                                                                                                                     |                      |                                        | 1        | l l     | 一一   |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------------------------------|----------|---------|------|

| characterist             | ic                                                                                                                                    | symbol               | Condition (Unless otherwise specified, | Standard | value   | unit |

|                          |                                                                                                                                       | 5,501                | VCC=5V, -<br>55°C≤TA≤125°C)            | Minimum  | Maximum | -    |

|                          | IOE data delay                                                                                                                        | tIOD                 |                                        |          | 0.6     | ns   |

|                          | IOE register control signal delay                                                                                                     | ¹IOC                 |                                        |          | 0.9     | ns   |

|                          | IOE Register Clock to Output<br>Delay                                                                                                 | <sup>t</sup> IOCO    |                                        |          | 0.5     | ns   |

|                          | IOE combination delay                                                                                                                 | tIOCOMB              |                                        |          | 0.0     | ns   |

|                          | The setup time of IOE register data and enable signal before the clock; The recovery time of IOE register after asynchronous clearing | tlOSU                |                                        | 3.5      |         | ns   |

|                          | IOE register data and enable signal hold time after clock                                                                             | tIOH                 |                                        | 1.9      |         | ns   |

| Input and output unit    | IOE register clear time                                                                                                               | <sup>t</sup> IOCLR   |                                        |          | 1.2     | ns   |

| IOE Timing<br>Parameters | Output Buffer and PAD Delay                                                                                                           | <sup>t</sup> OD1     | slow slew<br>rate=off,C1=35pF          |          | 3.6     | ns   |

|                          | Output Buffer and PAD Delay                                                                                                           | tOD3                 | slow slew rate=on,<br>C1=35pF          |          | 8.3     | ns   |

|                          | IOE output buffer disable delay                                                                                                       | <sup>t</sup> XZ      |                                        |          | 5.5     | ns   |

|                          | IOE output buffer enable delay                                                                                                        | <sup>t</sup> ZX1     | slow slew rate=off,<br>C1=35pF         |          | 5.5     | ns   |

|                          | IOE output buffer enable delay                                                                                                        | tZX3                 | slow slew rate=on,<br>C1=35pF          |          | 10.2    | ns   |

|                          | IOE input pad and buffer to IOE register delay                                                                                        | <sup>t</sup> INREG   |                                        |          | 10.0    | ns   |

|                          | IOE register feedback delay                                                                                                           | <sup>1</sup> IOFD    |                                        |          | 4.0     | ns   |

|                          | IOE input pad and buffer to fast interconnect delay                                                                                   | tINCOMB              |                                        |          | 4.0     | ns   |

|                          | Combination input data or address to EAB delay                                                                                        | <sup>t</sup> EABDATA |                                        |          | 1.9     | ns   |

| Т | iming     | Register input data or address to EAB delay                  | <sup>'</sup> EABDATA  |  |     | 6.0  | ns |   |

|---|-----------|--------------------------------------------------------------|-----------------------|--|-----|------|----|---|

| P | arameters | Combinatorial Input Write<br>Enable to EAB Delay             | tEABWE1               |  |     | 1.2  | ns |   |

|   |           | Register input write enable to EAB delay                     | <sup>t</sup> EABWE2   |  |     | 6.2  | ns |   |

|   |           | EAB Register Clock Delay                                     | tEABCL                |  |     | 2.2  | ns |   |

|   |           | EAB Register Clock to Output<br>Delay                        | tEABCO                |  |     | 0.6  | ns |   |

|   |           | Bypass Register Delay                                        | <sup>t</sup> EABBYPAS |  |     | 1.9  | ns |   |

|   |           | EAB register setup time                                      | tEABSU                |  | 1.8 |      | ns |   |

|   |           | EAB register hold time                                       | 'EABH                 |  | 2.5 |      | ns |   |

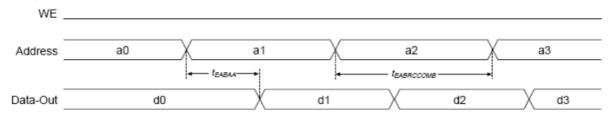

|   |           | Address access delay                                         | <sup>t</sup> AA       |  |     | 10.7 | ns |   |

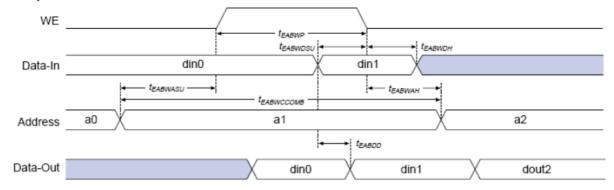

|   |           | Write pulse width                                            | <i>t</i> WP           |  | 7.2 |      | ns |   |

|   |           | Data setup time before the falling edge of the write pulse   | WDSU.                 |  | 2.0 |      | ns |   |

|   |           | Data hold time after the falling edge of the write pulse     | tWDJ                  |  | 0.4 |      | ns |   |

|   |           | Address setup time before the rising edge of the write pulse | tWASU                 |  | 0.6 |      | ns |   |

|   |           | Address hold time after the falling edge of the write pulse  | ₩.A.H.                |  | 1.2 |      | ns |   |

|   |           | Write Enable to Data Output<br>Valid Delay                   | tWO                   |  |     | 6.2  | ns |   |

|   | sd        | Data input to data output valid delay                        | <sup>t</sup> DD       |  |     | 6.2  | ns |   |

| Ī | Data outp | out delay                                                    | <i>t</i> EABOUT       |  | 0.6 | ns   |    | • |

| Data output delay | tEABOUT            |     | 0.6 | ns |

|-------------------|--------------------|-----|-----|----|

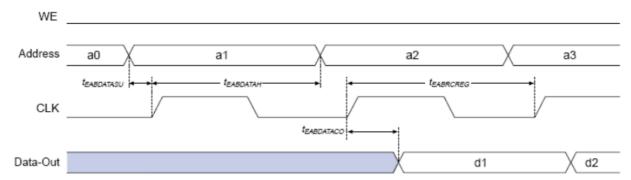

| Clock high time   | tEABCH             | 4.0 |     | ns |

| Clock low time    | <sup>t</sup> EABCL | 7.2 |     | ns |

| characteristic                     |                              |                                    | Condition (Unless otherwise specified | Standard | unit    |      |

|------------------------------------|------------------------------|------------------------------------|---------------------------------------|----------|---------|------|

| characteristic                     |                              | symbol VCC = 5V<br>-55°C≤TA≤125°C) |                                       | Minimum  | Maximum | unit |

|                                    | EAB address access delay     | <sup>t</sup> EABA                  |                                       |          | 17.0    | ns   |

| Embedded                           | ,                            | tEABRCCO                           |                                       | 17.0     |         | ns   |

| Array Block<br>EAB macro<br>timing |                              | EABRCRE                            |                                       | 11.9     |         | ns   |

|                                    | EAB write pulse width        | <i>t</i> EABWP                     |                                       | 7.2      |         | ns   |

|                                    | EAB asynchronous write cycle | tEABWCCO                           |                                       | 9.0      |         | ns   |

|                      | EAB Synchronous Write Cycle                                                                                | <sup>t</sup> EABWCRE | 16.0 |      | ns  |

|----------------------|------------------------------------------------------------------------------------------------------------|----------------------|------|------|-----|

|                      | EAB data input to data output                                                                              | LABWORL              | 10.0 |      | 113 |

|                      | valid delay                                                                                                | <i>t</i> EABDD       |      | 12.5 | ns  |

|                      | EAB clock to output delay when using output registers                                                      | EABDATAC             |      | 3.4  | ns  |

|                      | When using input registers, EAB data/address, setup time before clock                                      | 'EABDATAS            | 5.6  |      | ns  |

|                      | When using input registers, EAB data/address, hold time after clock                                        | <i>t</i> EABDATA     | 0.0  |      | ns  |

|                      | When using the input register, EAB write enable is set up before the clock                                 | <i>t</i> EABWES      | 5.8  |      | ns  |

|                      | When using the input register,<br>EAB write enable is enabled,<br>and the hold time after the clock        | <sup>t</sup> EABWEH  | 0.0  |      | ns  |

|                      | The setup time of EAB data before the falling edge of the write pulse when the input register is not used  | <sup>t</sup> EABWDS  | 5.8  |      | ns  |

|                      | When the input register is not used, the EAB data is held after the falling edge of the write pulse.       | <i>t</i> EABWDH      | 0.0  |      | ns  |

|                      | When the input register is not used, the EAB address setup time before the falling edge of the write pulse | tEABWAS              | 2.7  |      | ns  |

|                      | When the input register is not used, the EAB address is held after the falling edge of the write pulse.    | <sup>'</sup> EABWAH  | 0.0  |      | ns  |

|                      | Delay from EAB write enable to data output valid                                                           | <sup>t</sup> EABWO   |      | 11.8 | ns  |

|                      | TCK clock cycle                                                                                            | tJCP                 | 100  |      | ns  |

|                      | TCK clock high level time                                                                                  | <sup>t</sup> JCH     | 50   |      | ns  |

|                      | TCK clock low level time                                                                                   | tJCL                 | 50   |      | ns  |

| JTAG<br>Timing       | JTAG port setup time                                                                                       | tJPSU                | 20   |      | ns  |

| Timing<br>Parameters | JTAG port hold time                                                                                        | <sup>t</sup> JPH     | 45   |      | ns  |

|                      | JTAG port clock to output                                                                                  | tJPCO                |      | 25   | ns  |

|                      | JTAG port high impedance to valid output                                                                   | <sup>t</sup> JPZX    |      | 25   | ns  |

|                      | JTAG port valid output to high impedance                                                                   | <sup>t</sup> JPXZ    |      | 25   | ns  |

|                                  | Capture register setup time                                                                                          | tJSSU                |                                                         | 20                  |       | ns   |

|----------------------------------|----------------------------------------------------------------------------------------------------------------------|----------------------|---------------------------------------------------------|---------------------|-------|------|

|                                  | Capture register hold time                                                                                           | <sup>t</sup> JSH     |                                                         | 45                  |       | ns   |

|                                  | Update register clock to output                                                                                      | tJSCO                |                                                         |                     | 35    | ns   |

|                                  | Update register high impedance to valid output                                                                       | tJSZX                |                                                         |                     | 35    | ns   |

| <b>asda</b> Table                | Update register valid output to high impedance                                                                       | <sup>t</sup> JSXZ    |                                                         |                     | 35    | ns   |

|                                  |                                                                                                                      |                      | a andition                                              | Ctondord            | value |      |

| characteristic                   |                                                                                                                      | symbol               | condition<br>(Unless<br>otherwise specified<br>VCC = 5V | Standard<br>Minimum |       | unit |

|                                  |                                                                                                                      |                      | 55°C≤TA≤125°C)                                          |                     |       |      |

|                                  | Dedicated input to IOE control input delay                                                                           | tDIN2IOE             |                                                         |                     | 10.2  | ns   |

|                                  | Dedicated clock to LE or EAB clock delay                                                                             | tDIN2LE              |                                                         |                     | 4.8   | ns   |

|                                  | Dedicated input to LE or EAB data delay                                                                              | <sup>t</sup> DIN2DAT |                                                         |                     | 7.2   | ns   |