# BSTM88512-55CB Static Memory Military Product Manual

## **Table of contents**

- Product Introduction

- Product Overview

- Features

- Product use and application range

- Corresponding replacement of foreign products

- Product appearance 2 Product Dimensions

- Product Photos and Logo Description

- Standard Implementation

- Brief description of basic working principle

- Circuit Function

- Pin Description

- Extreme and recommended operating conditions

- Extreme working conditions

- Recommended operating conditions

- Main technical parameters

- Electrical characteristics parameters

- Application Guide

- Key parameter timing diagram/typical application peripherals

- ESDcharacteristic

- Radiation resistance

- Identification and diagnosis of common problems

- Notes

- Product transportation and storage precautions

- 2Product unpacking and inspection

- Circuit Operation Precautions

- Illustrate

- After-sales service and garante

- Contact information

- Version and Disclaimer

## I. Product Introduction

#### 1.1. Product Overview

BSTM88512-55CBIs a low power asynchronous single chip SRAM, the storage capacity is512Kx8bits, and the access time is55ns.

Device Adoption8Bidirectional data port, can read and write8bit data. Input and output compatible TTL Level.

#### 1.2. Product Features

The main technical indicators are as follows:

- Operating Voltage:5V±0.5V

- Storage capacity:4Mbit (512kx8bit)

- Reading speed: ≤55ns

- Input high level: ≥2.2V

- Input low level: ≤0.8V

- -Package:CDIP32

- Operating temperature: -55°C ~ +125°C

• Storage temperature: -65°C ~ +150°C

## 1.3. Product use and application range

BSTM88512-55CBThis circuit is a4MAsynchronous single port SRAM, used as a high-speed cache with the master control device,

It is widely used in communication modules.

## 1.4. Corresponding to the situation of replacing foreign products

BSTM88512-55CBType static memory circuit and Microsemi Company EDI88512CA55CB Circuit compatible.

See the Appendix for parameter difference comparison1.

## II. Product appearance

#### 2.1. Product size

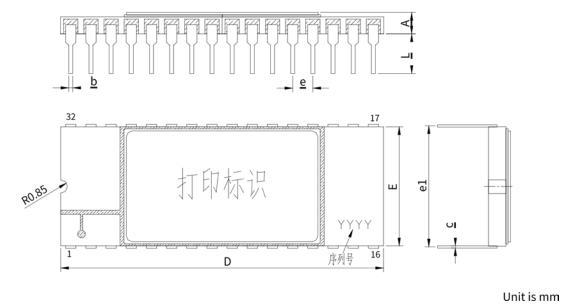

Device Adoption32leadDIPCeramic dual in-line package, dimensions as shown in the figure1regulations.

Figure 1. Dimensions

| DIMENSION | NUMBERVALUE |         |         |  |  |  |  |

|-----------|-------------|---------|---------|--|--|--|--|

| SYMBOLS   | MINIMUM     | NOMINAL | MAXIMUM |  |  |  |  |

| А         | 2.45        | _       | 3.05    |  |  |  |  |

| b         | 0.42        | _       | 0.58    |  |  |  |  |

| С         | 0.20        | _       | 0.30    |  |  |  |  |

| D         | 40.24       | _       | 41.04   |  |  |  |  |

| E         | 14.74       | _       | 15.24   |  |  |  |  |

| е         | _           | 2.54    | _       |  |  |  |  |

| e1        | _           | 15.24   | _       |  |  |  |  |

| L         | 4.50        | _       | 5.50    |  |  |  |  |

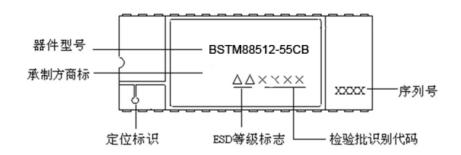

## 2.2. Product photos and logo descriptions

Picture 2. Device identification diagram

## **III. Standard Implementation**

This product is in accordance with Q/FC 20925-2022 Semiconductor Integrated Circuits BSTM88512-55CB Type Static Memory Circuit All content meets the requirements GJB 597B-2012,GJB548B-2005The reliability assurance level meets the requirements of JB 597B-2012 RegulationsB Level requirements.

## IV. Brief description of basic working principle

## 4.1. Circuit Function

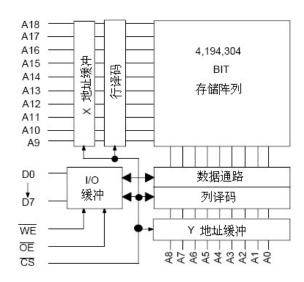

Picture 3. Functional Block Diagram

The device is a low-power asynchronous single-chip SRAM, the storage capacity is512Kx8bits, and the access time is55nslt uses

8Bidirectional data pin, can read and write8bit data. Its input and output levels are TTL Level compatible.

| OE | CS | WE | WORKING MODE   | OUTPUT          |

|----|----|----|----------------|-----------------|

| Х  | Н  | Х  | Low Power Mode | High resistance |

| Н  | L  | Н  | Output Cancel  | High resistance |

| L  | L  | Н  | Read Data      | Data Output     |

| Х  | L  | L  | Writing Data   | Data Writing    |

**Truth Table**

## 4.2. Pin Description

The lead-out terminals should be arranged as shown in the figure4regulations.

Picture 4. Terminal arrangement diagram

| PIN<br>NUMBER | ACHIEVEMENT<br>ABLE | I/O | SYMBOL | PIN<br>NUMBER | ACHIEVEMENT<br>ABL | I/O | SYMBOL |

|---------------|---------------------|-----|--------|---------------|--------------------|-----|--------|

| 1             |                     | I   | A18    | 17            |                    | I/O | D3     |

| 2             |                     | I   | A16    | 18            |                    | I/O | D4     |

| 3             |                     | I   | A14    | 19            | Data Bus           | I/O | D5     |

| 4             |                     | I   | A12    | 20            |                    | I/O | D6     |

| 5             |                     | 1   | A7     | 21            |                    | I/O | D7     |

| 6             | Address Bus         | 1   | A6     | 22            | Chip Select        | 1   | cs_    |

| 7             |                     | I   | A5     | 23            | Address Bus        | I   | A10    |

| 8             |                     | 1   | A4     | 24            | Output Enable      | 1   | OE_    |

| 9             |                     | 1   | А3     | 25            | Address Bus        | 1   | A11    |

| 10            |                     | 1   | A2     | 26            | Address Dos        | 1   | A9     |

|               |                     |     |        |               | Address Bus        |     |        |

| 11            |                     | 1   | A1     | 27            |                    | 1   | A8     |

| 12            |                     | 1   | A0     | 28            |                    | 1   | A13    |

| 13            | Data Bus            | I/O | D0     | 29            | Write Enable       | 1   | WE     |

| 14            | Data Bus            | I/O | D1     | 30            | Address Bus        | I   | A17    |

|    |      |     |     |    | Address Bus  |     |     |

|----|------|-----|-----|----|--------------|-----|-----|

| 15 |      | I/O | D2  | 31 |              | I   | A15 |

| 16 | land | GND | GND | 32 | power supply | VCC | VCC |

|    |      |     |     |    |              |     |     |

## V. Extreme working conditions and recommended working conditions

## 5.1.Extreme working conditions

Supply voltage (VDD.....0.5V~7V

Maximum power consumption (PD.....1W

Working power consumption (PD1.....350mW

Standby power consumption (PD2.....40mW

Storage temperature range (Tsj.....65°C~150°C

Maximum lead soldering temperature (Th) (10s).....300°C

Maximum Junction Temperature (Tj.....175°C

## 5.2. Recommended operating conditions

Supply voltage (VDD.....4.5V~5.5V

Working environment temperature (TA.....55°C~125°C

## VI. Main technical parameters

## 6.1. Electrical characteristics parameters

Table 2Electrical properties

|                              |        | STRIPITEM UNLESS                                                                | LIMIT VALU |         |      |

|------------------------------|--------|---------------------------------------------------------------------------------|------------|---------|------|

| CHARACTERISTIC               | SYMBOL | OTHERWISE SPECIFIED<br>VCC=5V                                                   | MINIMUM    | MAXIMUM | UNIT |

| Standby Supply Current (TTL) | ISB1   | - 55°C≤Ta≤125°C  \overline{CS} \Rightarrow Vih, Vin \Rightarrow Vih, Vcc  =5.5V | _          | 60      | mA   |

| Full standby supply current                               | ISB2  | CS≥VCC-0.2V,VIN≤0.2V or VIN≥VCC-0.2V,VCC=5.5V |          | 25       | mA |

|-----------------------------------------------------------|-------|-----------------------------------------------|----------|----------|----|

| Input high level voltage                                  | VIH   | _                                             | 2.2      | <u> </u> | V  |

| Input low level voltage                                   | VIL   | _                                             | <u> </u> | 0.8      | V  |

| Input high level current                                  | ILI-H | VCC=5.5V, VIH=5.5V                            | <u> </u> | 10       | μA |

| Input low level current                                   | ILI-L | VCC=5.5V, VIH=0V                              | <u> </u> | 10       | μA |

| Output high level voltage                                 | VOH   | IOH=-4.0mA                                    | 2.4      |          | V  |

| Output low level voltage                                  | VOL   | IOL=6mA                                       | <u> </u> | 0.4      | V  |

| Output high level leakage current                         | ILO-H | VCC=5.5V, CS=VIH<br>VI/O=5.5V,OE=VIH,         | _        | 10       | μА |

| Output low level leakage current                          | ILO-L | V=CC5.5V,CS=VIH<br>VI/O=0V,OE=VIH             | _        | 10       | μА |

| Working current                                           | ICC   | CS, WE=V,IILI/O=0mA,<br>f=18MHz,VCC=5.5V      | _        | 225      | mA |

| Functional testing                                        |       | f=18MHz,<br>VCC=4.5V,5V,5.5V                  | _        | _        | _  |

|                                                           | I     | Read Timing                                   |          |          | ı  |

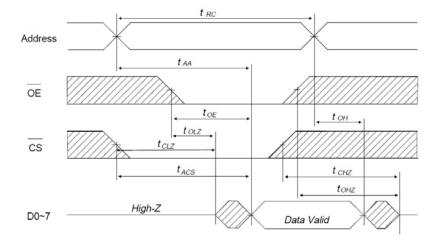

| Read Cycle                                                | tRC   | See picture5                                  | 55       | _        | ns |

| Address access time                                       | tAA   | See picture5                                  | _        | 55       | ns |

| Chip select to output data valid time                     | tACS  | See picture5                                  | _        | 55       | ns |

| Chip select to output low high impedance effective time   | tCLZ  | See picture5                                  | 3        | _        | ns |

| Data hold time after address change                       | tOH   | See picture5                                  | 0        | _        | ns |

| Output enable to data output valid time                   | tOE   | See picture5                                  | _        | 30       | ns |

| Output enable to output low high impedance effective time | tOLZ  | See picture5                                  | 0        | _        | ns |

|                                     |      | Write Timing           |    |    |    |

|-------------------------------------|------|------------------------|----|----|----|

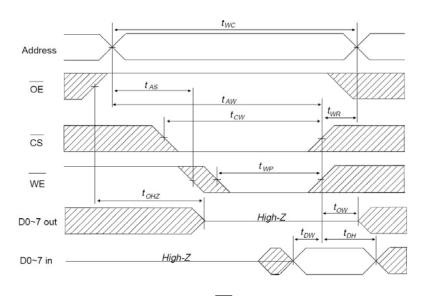

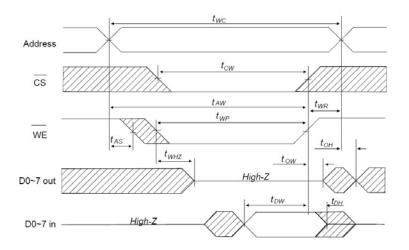

| Write cycle                         | tWC  | See picture6, picture7 | 55 | _  | ns |

| Chip select to write end time       | tCW  | See picture6, picture7 | _  | 50 | ns |

| Address creation time               | tAS  | See picture6, picture7 | 0  | _  | ns |

| Address valid to write end time     | tAW  | See picture6, picture7 | _  | 50 | ns |

| Write pulse width                   | tWP  | See picture6, picture7 | _  | 45 | ns |

| Write recovery time                 | tWR  | See picture6, picture7 | 0  | _  | ns |

| Data retention time                 | tDH  | See picture6, picture7 | 0  | _  | ns |

| Write to output high impedance time | tWIZ | See picture6, picture7 | 0  | 30 | ns |

| Data to write end time              | tDW  | See picture6           | _  | 30 | ns |

| Data to wine one time               | tDW  | See picture7           | -  | 40 | ns |

# VII. Application Guide

## 7.1. Key parameter timing diagram/typical application peripherals

Figure 5. Read circle

Figure 6 Write cycle 1 (CScontrol)

Figure 7. Write cycle 2 (VE control)

## 7.2. ESD characteristic

ESDThe levels are:2class,2000V 7.3

Radiation resistance none

## 7.4. Identification and diagnosis of common problems

This product is a static random access memory. The device data is uncertain after poweron and should not be used directly for certain deterministic data reading.

After power-on, the data writing operation should be performed, and the device reads data and verifies it based on the written data.

## VIII. Precautions

### 8.1. Product transportation and storage precautions

The chip storage environment temperature is: -65°C~+150°CUse designated anti-static packaging boxes to package and transport products.

During transportation, ensure that the chip does not collide with foreign objects. This product should be placed in an air-conditioned environment with temperature and humidity control.

In an environment to prevent the pins from being oxidized due to long-term storage, which will affect solderability.

## 8.2. Product unpacking and inspection

When unpacking and using the chip, please pay attention to the product logo on the chip shell. Make sure the product logo is clear, without stains, or scratches.

At the same time, pay attention to check the chip shell and pins. Make sure the shell is not damaged, without scratches, and the pins are neat, not missing, and not deformed.

#### 8.3. Circuit Operation Precautions

This product is an electrostatic sensitive device and should be installed in strict accordance with the electrostatic sensitive device operating requirements specified in relevant national standards and operation.

During the installation of this product, it is forbidden to touch or weld this type of product without tools such as anti-static wrist straps. Bare hands are not allowed to touch the external leads of the product.

Installation and use must be in an anti-static work area (equipped with an anti-static workbench, tables and chairs, etc.) equipped with an ion fan and operate within the

effective range of the ion blower.

Operators must receive anti-static training and wear anti-static work clothes (including antistatic gloves or finger cots, hats, work

Wear anti-static shoes and an anti-static wrist strap) and avoid any actions or operations that may easily generate static electricity.

The anti-static equipment (such as wrist straps and finger cots, etc.) should be tested regularly to ensure that qualified equipment is used before each use.

#### Anti-static facilities.

Devices should be stored in containers made of conductive materials (e.g., special boxes for integrated circuits).

Avoid using plastic, rubber or silk fabrics that may cause static electricity during transportation.

Ensure the relative temperature and humidity in the anti-static work area.

Use strictly in accordance with the recommended operating conditions. Using this product beyond the absolute maximum ratings may cause permanent damage to the product. bad.

If the system is used in an environment with high temperature and vibration requirements, it is recommended to take reinforcement measures on the circuit to improve its resistance to mechanical changes.

Ability to withstand mechanical vibration and thermal stress.

### IX. Illustrate

#### 9. Contact Details

Company Name: Beijing Star electronic technology Co. ltd.

Address: Room 0806,7th Floor, No.9 Dongsanhuan Zhonglu, Chaoyang District, Beijing China.

District Phone: +8613121851419

Website: https://beijing-est.cn/ e-mail: sales@beijing-est.cn

## X. Disclaimer:

We are only responsible for the current validity of this product manual when it is issued, and we will not notify you of any version update.

For the latest information, please contact us using the contact information in Article 9.2.

All technical information contained in this product manual is only for users to have a preliminary understanding of this product.

If there is any discrepancy between the product detailed specifications, the product detailed specifications shall prevail.

## XI. Appendix Parameter Comparison Table

Table 1. BSTM88512-55CBDetailed specifications and Microsemicompany EDI88512CA55CBD ifference comparison table

|                                            | SYMBOL | FOREIGN SPECIFICATION PARAMETERS PARAMETERS |         | UNIT    | IN SONOLUGION  |    |            |

|--------------------------------------------|--------|---------------------------------------------|---------|---------|----------------|----|------------|

|                                            |        | MINIMUM                                     | MAXIMUM | MINIMUM | MAXIMUM        |    | CONCLUSION |

| Standby<br>Supply<br>Current<br>(TTL)      | ISB1   | _                                           | 60      | _       | characteristic | mA | same       |

| Full<br>standby<br>supply<br>current       | ISB2   | _                                           | 25      | _       | 25             | mA | same       |

| Input high<br>level<br>voltage             | VIH    | 2.2                                         |         | 2.2     | _              | V  | same       |

| Input low<br>level<br>voltage              | VIL    | _                                           | 0.8     | _       | 0.8            | V  | same       |

| Input high<br>level<br>current             | ILI-H  | _                                           | 10      | _       | 10             | μA | same       |

| Input low<br>level<br>current              | ILI-L  | _                                           | 10      | _       | 10             | μA | same       |

| Output<br>high level<br>voltage            | VOH    | 2.4                                         |         | 2.4     |                | V  | same       |

| Output low<br>level<br>voltage             | VOL    | _                                           | 0.4     | _       | 0.4            | V  | same       |

| Output<br>high level<br>leakage<br>current | ILO-H  | _                                           | 10      | _       | 10             | μΑ | same       |

| Output low<br>level<br>leakage<br>current  | ILO-L  | _                                           | 10      | _       | 10             | μΑ | same       |

| Working current                                           | ICC   | _  | 225 | _  | 225 | mA | same |

|-----------------------------------------------------------|-------|----|-----|----|-----|----|------|

| Read<br>Cycle                                             | tRC   | 55 | _   | 55 | _   | ns | same |

| Address<br>access<br>time                                 | tAA   | _  | 55  | _  | 55  | ns | same |

| Output enable to data output valid time                   | tOE   | _  | 30  | _  | 30  | ns | same |

| Write<br>pulse<br>width                                   | tWP   | _  | 45  | _  | 45  | ns | same |

| Write cycle                                               | tWC   | 55 | _   | 55 | _   | ns | same |

| Chip<br>select to<br>output<br>data valid<br>time         | tACS  | _  | 55  | _  | 55  | ns | same |

| Data hold<br>time after<br>address<br>change              | tOH   | 0  | _   | 0  | _   | ns | same |

| Chip select to output low high impedance effective time   | tCLZ  | 3  | _   | 3  | _   | ns | same |

| Output enable to output low high impedance effective time | tOLZ  | 0  | _   | 0  | _   | ns | same |

| Chip<br>select to<br>output<br>high<br>impedance          | tZGar | 0  | 20  | 0  | 20  | ns | same |

| effective<br>time                                     |      |   |    |   |    |    |      |

|-------------------------------------------------------|------|---|----|---|----|----|------|

| Output enable to output high impedance effective time | tOHZ | 0 | 20 | 0 | 20 | ns | same |

| Chip<br>select to<br>write end<br>time                | tCW  | _ | 50 | _ | 50 | ns | same |

| Address<br>valid to<br>write end<br>time              | tAW  | _ | 50 | _ | 50 | ns | same |

| Address<br>creation<br>time                           | tAS  | 0 | _  | 0 | _  | ns | same |

| Write<br>recovery<br>time                             | tWR  | 0 | _  | 0 | _  | ns | same |

| Data<br>retention<br>time                             | tDH  | 0 | _  | 0 | _  | ns | same |

| Write to output high impedance time                   | tWIZ | 0 | 30 | 0 | 30 | ns | same |

| Data to<br>write end                                  | tDW  | _ | 40 | _ | 40 | ns | same |

| time                                                  | tDW  | _ | 30 | _ | 30 | ns | same |

| Output valid until writing is completed               | tWlq | 0 | _  | 0 | _  | ns | same |