8-12GHz

# **BSTGPA92-0812** 8-12GHz GaN Power Amplifier **Data Sheet**

#### I. Product Introduction

BSTGPA92-0812 is a high-performance GaN power amplifier chip with a frequency range of 8 to 12 GHz and can operate in both pulsed and continuous wave modes. In pulsed mode, it achieves a small signal gain of 31.5 dB, a saturated output power of 46.5 dBm, and a poweradded efficiency of 44%. This chip utilizes on-chip through-hole metallization to ensure good grounding, eliminating the need for additional grounding measures and making it easy to use.

The back side is metallized and suitable for eutectic sintering process.

### **II. Key Technical Indicators**

Frequency range: • Small signal gain (Pulse): 31.5dB • Saturated output power (Pulse): 46.5dBm • Power added efficiency (Pulse): 44% • Power gain (Pulse): 22dB Input return loss: -14dB Quiescent operating current (Pulse): 1.64A @+28V Chip size: 4.00mm × 4.00mm × 0.075mm

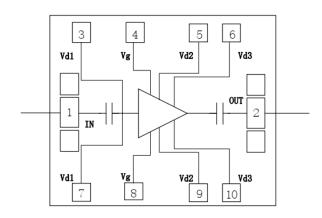

## **II. Functional Block Diagram**

Figure 1.

### **III. Electrical Performance**

Table 1. ( $T_A = +25^{\circ}C$ ,  $V_{d1} = V_{d2} = V_{d3} = +28V$ ,  $V_g = -2.6V$ , Pulse Mode)

| PARAMETER NAME                | SYMBOL | MINIMUM | TYPICAL<br>VALUES | MAXIMUM | UNIT |

|-------------------------------|--------|---------|-------------------|---------|------|

| Frequency range               | Freq   | 8       | _                 | 12      | GHz  |

| Small signal gain             | Gain   | 30      | 31.5              | 33.8    | dB   |

| Saturated output power        | Psat   | 45.7    | 46.5              | 47      | dBm  |

| Power added efficiency        | PAE    | 40      | 44                | 50      | %    |

| Power gain                    | Gp     | 21.5    | 22                | 23      | dB   |

| Input return loss             | RL_IN  | _       | -14               | -7      | dB   |

| Dynamic current               | IDD    | _       | 3.4               | 4       | А    |

| Quiescent operating current * | IDQ    | _       | 1.64              | 1.88    | Α    |

<sup>\*</sup>Adjust Vg within the -3V to -2.4V range to achieve a pulse quiescent current of 1.64A. Reference Vg values: -2.6V for pulse, -2.6V for CW.

## IV. Absolute Maximum Ratings

Table 2.

| PARAMETER                       | VALUE        |

|---------------------------------|--------------|

| Maximum drain operating voltage | +40V         |

| Maximum gate operating voltage  | -5V          |

| Maximum input power             | +30dBm       |

| Storage temperature             | -65°C~+150°C |

| Operating temperature           | -55°C~+125°C |

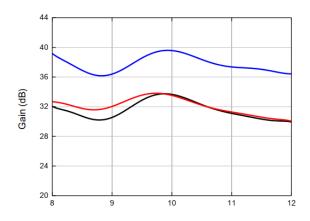

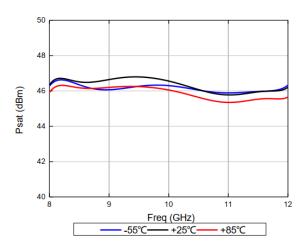

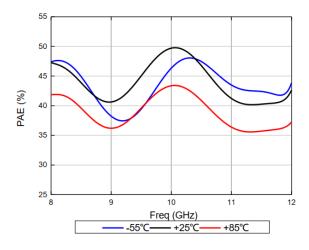

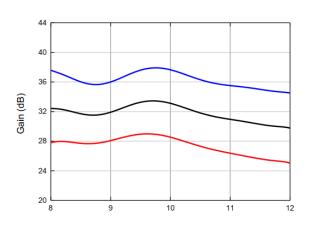

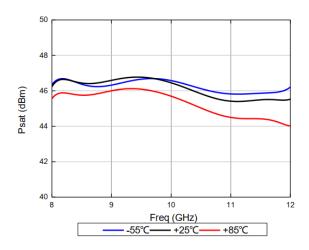

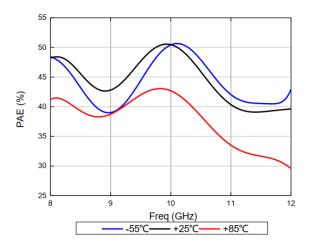

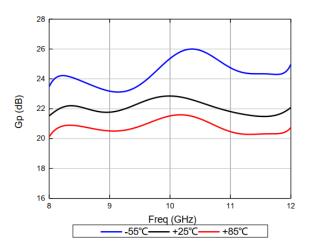

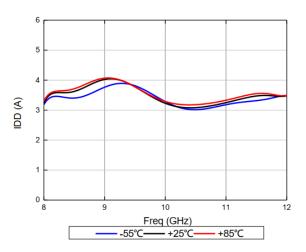

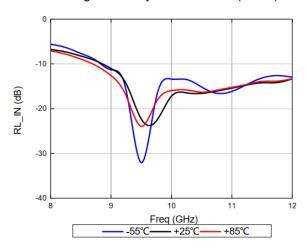

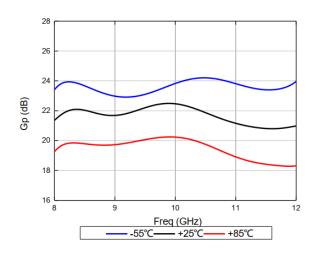

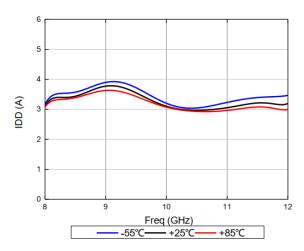

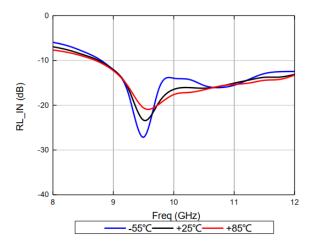

# V. Test curve ( $V_g$ =-2.6V, $V_{d1}$ = $V_{d2}$ = $V_{d3}$ =+28V, pulse test conditions: pulse width 1ms, duty cycle 10%)

Figure 2. Small signal gain (Pulse)

Figure 4. Saturated output power (Pulse)

Figure 6. Power added efficiency (Pulse)

Figure 3. Small Signal Gain (CW)

Figure 5. Saturated output power (CW)

Figure 7. Power added efficiency (CW)

Figure 8. Power gain (Pulse)

Figure 10. Dynamic current (Pulse)

Figure 12. Input return loss (Pulse)

Figure 9. Power gain (CW)

Figure 11. Dynamic current (CW)

Figure 13. Input return loss (CW)

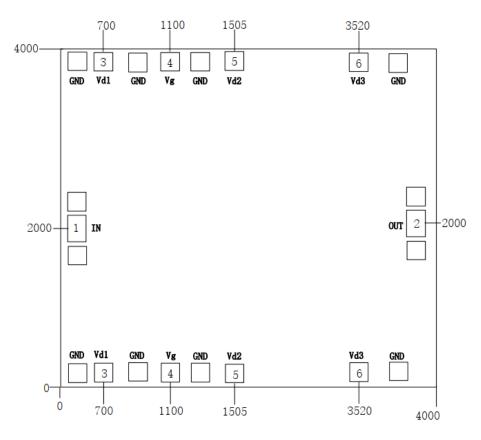

## VI. Chip Port Diagram (unit: μm)

Figure 14.

### 6.1. Port Definition

| SERIAL<br>NUMBER | PORT NAME | DEFINITION                                                        | SIGNAL OR<br>VOLTAGE |

|------------------|-----------|-------------------------------------------------------------------|----------------------|

| 4                | Vg        | Negative power supply, it is recommended to add a 100pF capacitor | -2.6V                |

| 3/5/6            | Vd1/2/3   | Positive power supply, it is recommended to add a 100pF capacitor | 28V                  |

| 1                | IN        | RF signal input terminal                                          | RF                   |

| 2                | OUT       | RF signal output terminal                                         | RF                   |

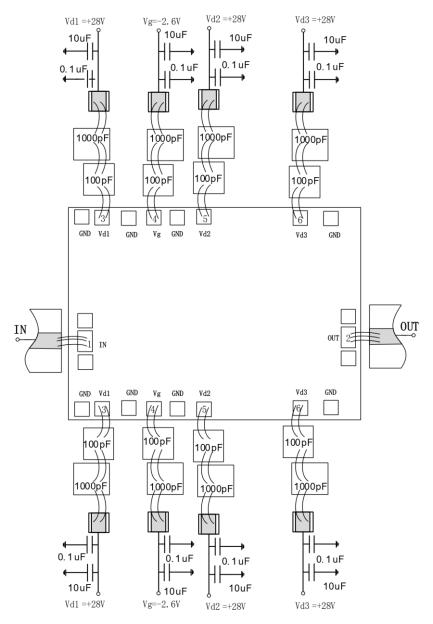

## VII. Recommended Assembly Drawing

Figure 15.

### **VIII. Notes**

- Assemble and use in a clean environment.

- GaN material is very brittle and the chip surface is easily damaged (do not touch the surface), so you must be careful when using it.

- Use three bonding wires (25µm diameter gold wire) for input and output. Keep the bonding wires as short as possible and no longer than 300µm.

- The sintering temperature should not exceed 300°C and the sintering time should be as short as possible, not exceeding 30 seconds.

- This product is an electrostatic sensitive device, please be careful to prevent static electricity during storage and use.

- Store in a dry, nitrogen environment.

- Do not attempt to clean the chip surface with dry or wet chemical methods.