# **BSTGPA12-0713**

7-13 GHz GaN Power Amplifier Data Sheet

#### **Product Introduction**

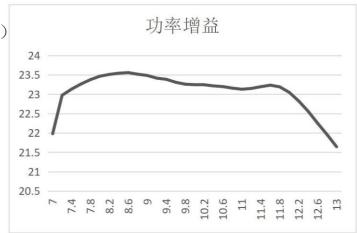

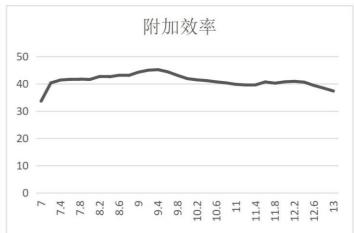

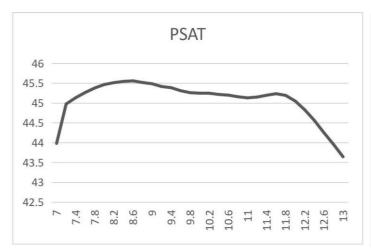

BSTGPA12-0713 Is a 0.25 $\mu$ m GaN amplifier chip made with HEM T technology. The operating frequency range covers 7.0 GHz to 13.0 GHz, the power gain is greater than 21.5 dB, the typical saturated output power is 45.5 dB m, the typical power added efficiency is 40 %, and it can operate in pulse /continuous wave mode. The chip is grounded through a back-side via, and the typical operating voltage is  $V_D = +28$  V,  $V_G = -2.5$  V.

### **Key technical indicators**

■ Frequency range: 7GHz~13GHz

■ Power Gain: 23.5dB

Saturated output power: 45.5dBm

■ Power added efficiency: 40%

■ Power supply: +28V

■ Chip size: 3.50 mm×3.20 mm×0.10 mm

#### **Application Areas**

- Microwave transceiver components

- Solid-state transmitter

## DC parameters (TA = +25 °C)

| Index                   | Symbol | Minimum | Typical Value | Maximum | Unit |

|-------------------------|--------|---------|---------------|---------|------|

| Gate operating voltage  | Vg     | - 3.0   | - 2.5         | - 2.4   | V    |

| Drain operating voltage | Vd     | -       | 28            | -       | V    |

| Quiescent Drain Current | ld     | -       | 1.7           | 2       | Α    |

| Dynamic drain current   | ldd    | -       | 2.5           | 3.0     | Α    |

| Dynamic gate current    | lgg    | -       | 3.0           | 10.0    | mA   |

## Microwave electrical parameters ( TA = +25 °C , Vd = +28V , Vg = -2.5V )

| index                  | Symbol            | Minimum    | Typical<br>Value | Maximum | Unit |

|------------------------|-------------------|------------|------------------|---------|------|

| Frequency range        | f                 | 7.0 ~ 13.0 |                  |         | GHz  |

| Saturated output power | P <sub>SAT</sub>  | 43.5       | 45.2             | -       | dBm  |

| Power Gain             | G₽                | 21.5       | -                | 23.5    | dB   |

| Power gain flatness    | △ G <sub>P</sub>  | -          | -                | ±1      | dB   |

| Power Added Efficiency | PAE               | 36         | -                | 47      | %    |

| Linear gain            | S <sub>21</sub>   | -          | 33               | -       | dB   |

| Linear gain flatness   | △ S <sub>21</sub> | -          | -                | ±3      | dB   |

| Input standing wave    | VSWR (in)         | -          | 1.6              | 2.0     | -    |

Note: All chips have been 100 % DC tested and 100 % RF tested on-chip;

### Limited use parameters

| parameter                                 | Symbol           | Limit value     |

|-------------------------------------------|------------------|-----------------|

| Maximum drain-source forward bias voltage | V <sub>D</sub>   | +32V            |

| Minimum gate negative bias                | V <sub>G</sub>   | - 5V            |

| Maximum input power                       | P <sub>IN</sub>  | +28dBm          |

| Storage temperature                       | T <sub>STG</sub> | -65 °C∼ +150 °C |

| Maximum operating channel temperature     | T <sub>OP</sub>  | +225 °C         |

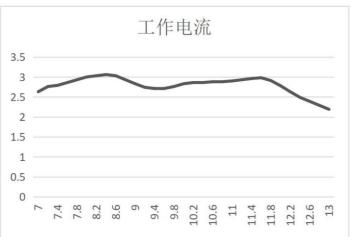

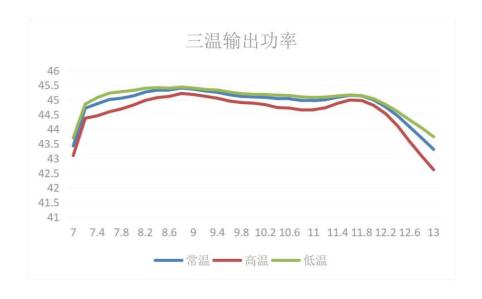

## Typical curve ( Vd=+28V , Vg= -2.5V , PIN=22dBm )

Three-temperature test: VD=28V, VG=-2.5V,Pin=22dBm , 10% duty cycle.

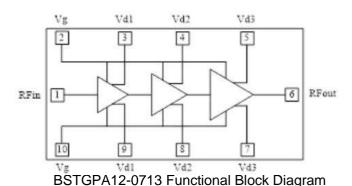

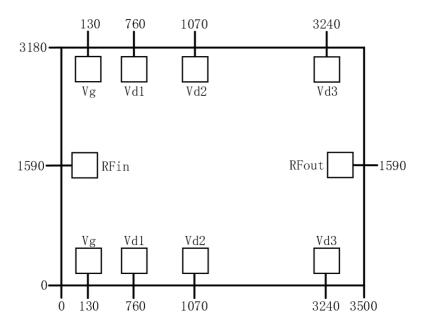

## **Chip port diagram**

## **Port Definition**

| Port Name   | Definition             | Signal or voltage |

|-------------|------------------------|-------------------|

| Vg          | Gate voltage           | - 2.5V            |

| Vd1/Vd2/Vd3 | Amplifier Power Supply | 28V               |

| RFin        | RF Input               | RF                |

| RFout       | RF Output              | RF                |

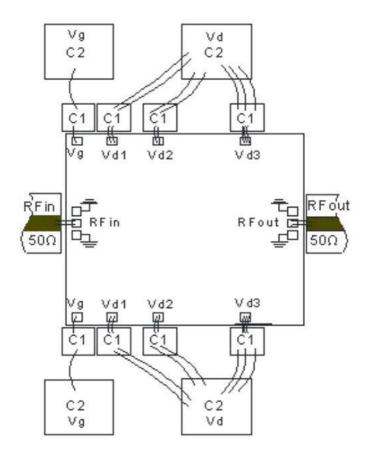

#### Recommended assembly drawing

#### Note:

- The capacitance of the external capacitor is C1=100pF, C2=1000pF

It is recommended to use a single-layer ceramic capacitor, where C1 It should be as close to the chip as possible, not exceeding 750µm.

- 2. Consider 125µm ~ 250µm

- The low-loss and low-dielectric constant microstrip line is bonded / sintered on the carrier to reduce transmission loss. The input and output bonding wire length is controlled at 350µm±150µm

- 3. Close to chip gate Vg a 10uf tantalum capacitor or electrolytic capacitor should be added.