# BST4VSX55 Series Product Manual

#### **Product Overview**

BST4VSX55 is a high-performance military FPGA with tens of millions of gates . The core power supply voltage of this FPGA is 1.2V , the I/O power supply voltage is 1.5  $\sim$  3.3V , and the system clock frequency can reach up to 400Mz . It has 55,296 programmable logic units and 24576 slices ; the storage resources include 384 distributed RAMs and 320 embedded 18Kb BRAMs ; the clock resources include 32 BUFGs , 32 pairs of global clock input pins, 8 DCMs , and 4 PMCDs ; there are 512 embedded DSPs ; the maximum number of available I/Os is 640 , which can also be used as 320 pairs of differential I/Os , the number of package pins is 1148 , and the ESD resistance is 2000V .

Its main parameters are as follows:

Table 1 BST4VSX55 main parameters

|           | Configurable logic blocks CLB |                 |             |                               | l 8일:li             | Memory Block<br>RAM |               | Digita<br>Mana   | Phas<br>clock         | Inpu<br>interf<br>group         | Maxi<br>numb<br>input      |

|-----------|-------------------------------|-----------------|-------------|-------------------------------|---------------------|---------------------|---------------|------------------|-----------------------|---------------------------------|----------------------------|

| product   | Array<br>RowX<br>List         | Logical<br>Unit | Slicenumber | Maximum<br>distribution(<br>) | al Signal<br>æssing | Modules             | maximum(<br>) | al Clock<br>ager | e-matched<br>dividers | ut and output<br>face<br>ptotal | mum per of user and output |

| BST4VSX55 | 128x48                        | 55296           | 24576       | 384                           | 512                 | 320                 | 5760          | 8                | 4                     | 13                              | 640                        |

#### **Functional Block**

Overall architecture

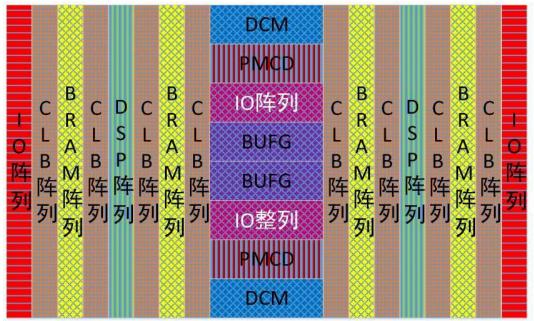

The functional block diagram of BST4VSX55 is shown in the figure :

Figure 1 BST4VSX55 functional block diagram

### Configurable logic blocks CLB

## **Ordering Information**

**Table 1 Ordering information**

| Product    | Lead     | Package  | Package   | Dimensions | weight |  |  |  |  |  |  |  |  |

|------------|----------|----------|-----------|------------|--------|--|--|--|--|--|--|--|--|

| Model      | material |          | Туре      | ( mm )     |        |  |  |  |  |  |  |  |  |

| BST4VSX55- | Sn10Pb90 | CF-      |           | 35*35*8.5  | W 29g  |  |  |  |  |  |  |  |  |

| 10CF1148M  |          | CCGA1148 |           |            |        |  |  |  |  |  |  |  |  |

| BST4VSX55- | SAC305   | FC-      | Non-      | 35*35*3.11 | < 11g  |  |  |  |  |  |  |  |  |

| 10FF1148   |          | BGA1148  | hermetic  |            | _      |  |  |  |  |  |  |  |  |

| BST4VSX55- | Pb37Sn63 |          | packaging |            |        |  |  |  |  |  |  |  |  |

| 10FF1148N  |          |          |           |            |        |  |  |  |  |  |  |  |  |