## BST14288 CPLD Product Brochure Ver . 5.3

#### **Product Overview**

BST14288 is a high-density, high-performance complex programmable logic device (CPLD) based on the "product term" principle, with 6400 available gates; core power supply voltage is 3.3V/5V, I/O voltage is 3.3V/5V; the number of logic arrays (FB) is 16, with 288 trigger resources; operating temperature range is -55°C~+125°C, Pinto-Pin maximum delay time: 10 ns, maximum system frequency is 93.3MHz; ESD protection is not less than 4000V.

Table 1Basic information of products

| Package          | C QFP208 (ceramic) | LQFP208 (Plastic) | C QFP 160 (Ceramic) |  |  |  |  |

|------------------|--------------------|-------------------|---------------------|--|--|--|--|

| Available        | 16                 | 133               |                     |  |  |  |  |

| Macrocell        | 2 88               |                   |                     |  |  |  |  |

| Available        | 6 400              |                   |                     |  |  |  |  |

| T PD (ns)        | 1 0                |                   |                     |  |  |  |  |

| F <sub>CNT</sub> |                    | 9 3.3             |                     |  |  |  |  |

#### **Product features**

- 5V in-system programming capability based on IEEE Std.1149.1 JTAG protocol;

- Compatible with Xilinx burning software IMPACT to perform JTAG operations on the chip;

- The core power supply voltage is 5V/3.3V, and the IO voltage is 5V/3.3V;

- Maximum pin delay of 10ns;

- 16 -bit counter frequency Fcnt (same FB) up to 93.3 MHz;

- In the same FB, 90 Product Terms can drive any macro cell (MC);

- The power consumption mode of each macro cell can be independently programmed to reduce its power consumption by 20% or more;

- Each output can configure its slew rate;

- Support hot-swap;

- ESD protection is greater than or equal to 4 000V;

- Macrocell registers can be programmed for independent clear, set, clock, and clock enable control;

- Programmable device encryption bits protect user designs;

- It has three invertible global clocks;

- Unconfigured pins can be configured to be grounded;

- Applications: These devices are widely used in applications such as bus bridging, I/O expansion, power-on reset (POR), timing control, and device initialization control.

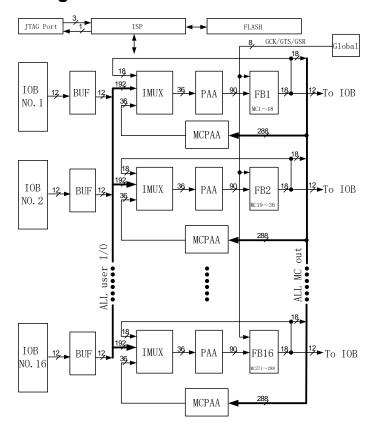

### **Functional Block Diagram**

Figure 1 BST14288 block diagram

# **Ordering Information**

| Product Model        | Quality  | Package | Lead                                 | Packaging | Detailed         | Product            |

|----------------------|----------|---------|--------------------------------------|-----------|------------------|--------------------|

|                      | Grade    |         | material                             | materials | specifications   | Status             |

| BST14288 MCPCQFP208  | Class B  | CQFP208 | Nickel<br>plating<br>Gold<br>plating | ceramics  | Q/BST 20304-2017 | Mass<br>production |

| BST14288-10MLQFP208N | N -level | QFP208  | Tinning                              | plastic   | Q/BST 20242-2015 | Mass production    |

| BST14288 -ACQFP160M1 | Class B  | CQFP208 | Nickel<br>plating<br>Gold<br>plating | ceramics  | Q/BST 50043-2021 | Mass<br>production |